This post is about working with layers in Eagle PCB. The sample design file that contains the schematic and gerber can be downloaded from Shapeoko's site here.

In this post, the layer descriptions are taken from Adafruit's site at https://learn.adafruit.com/ktowns-ultimate-creating-parts-in-eagle-tutorial/creating-a-package-outline. The photos are taken from the gerber file obtained from the Shapeoko site mentioned above.

Overview

Layer 1 (Top)

This layer is used to draw pads on the top of the PCB. The SMD tool (to create pads) generally uses layer 1 to indicate which side of your PCB the pad should be placed on, though in very rare circumstances you may need to use layer 16 as well:

Layer 16 (Bottom)

This layer is used to draw pads on the bottom of the PCB. In very rare circumstances this layer may be used to draw pad for SMD.

Layer 2 ~ 15

These layers could be accessed when working on multi-layer boards using professional version of Eagle.

Layer 17 (Pads)

Layer 18 (Vias)

Layer 19 (Unrouted)

Layer 20 (Dimension)

Layer 21 (tPlace)

This layer is used to draw lines that will be rendered as the silk screen on your PCBs (the printed text/lines/shapes we see).

The Line Tool can draw lines on any layer, but it's particularly important to this layer (and Layer t51 (tDocu)).

Layer 23 (tOrigins)

Layer 25 (tNames)

This layer is used to hold the unique 'names' for each part on your PCB (ex. C1, R5, X12, etc.).

Layer 27 (tValues)

This layer is used to hold the value for each part (such as 10K, 0.1µF, AT86RF212, etc.).

Layer 29 (tStop)

Layer 30 (bStop)

Layer 44 (vRestrict)

Layer 49 (Reference)

Layer 51 (tDocu)

This layer is used for documentation purposes, such as drawing the mechanical dimensions of your part (more on that shortly!). Normally this layer isn't printed on the PCBs, but it's very important for documentation and for PCB design.

The Line Tool can draw lines on any layer, but it's particularly important to this layer (and Layer 21 (tPlace)).

Note,

By enabling Layer 16 (Bottom), Layer 17 (Pads), and Layer 21 (tPlace) we could get a pretty good picture of the PCB. As for Layer 25 (tNames), it needs to be cleaned up (removing unwanted names, labels, markings, etc.) before it could be added to the final design submitted to the PCB manufacturer for PCB making.

Layer 25 (tNames)

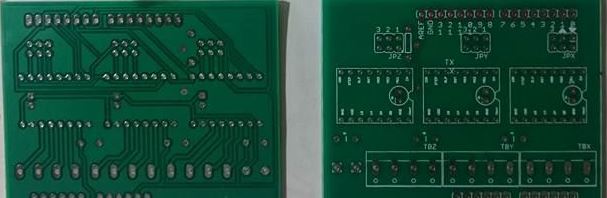

Below is the gerber file sent by the PCB manufacturer for confirmation. It's the combination of Layer 1 (Top), Layer 16 (Bottom), Layer 17 (Pads), Layer 21 (tPlace) and Layer 25 (tName).

The PCB developed.

Important!!

There is an error in the layout that causes the GND and the 12V (see photos below) to short. For the already developed PCB, this error can be fixed by cutting the GND trace that crosses the 12V trace with a knife.

The steps for removing this trace in the layout file are as follow:

1. Zoom in to the problem spot and left click on the Ripup icon.

2. Left click on the signal to be ripped up.

3. Click on the signal once again to remove it completely.

Reference:

An Introduction to Layers in Eagle

No comments:

Post a Comment